Контроллер последовательного интерфейса что это

Контроллер последовательного интерфейса что это

Использование последовательных линий связи для обмена данными с внешними устройствами возлагает на контроллеры ВУ дополнительные по сравнению с контроллерами для параллельного обмена функции. Во-первых, возникает необходимость преобразования формата данных: из параллельного формата, в котором они поступают в контроллер ВУ из системного интерфейса микроЭВМ, в последовательный при передаче в ВУ и из последовательного в параллельный при приеме данных из ВУ. Во-вторых, требуется реализовать соответствующий режиму работы внешнего устройства способ обмена данными: синхронный или асинхронный.

Синхронный последовательный интерфейс

Простой контроллер для синхронной передачи данных в ВУ по последовательной линии связи (последовательный интерфейс) представлен на рис. 3.7.

Рис. 3.7. Контроллер последовательной синхронной передачи

Восьмиразрядный адресуемый буферный регистр контроллера А1 служит для временного хранения байта данных до его загрузки в сдвиговый регистр. Запись байта данных в буферный регистр с шины данных системного интерфейса производится так же, как и в параллельном интерфейсе (см. Параллельная передача данных и рис. 3.5), только при наличии единицы в одноразрядном адресуемом регистре состояния контроллера А2. Единица в регистре состояния указывает на готовность контроллера принять очередной байт в буферный регистр. Содержимое регистра А2 передается в процессор по одной из линий шины данных системного интерфейса и используется для формирования управляющего сигнала системного интерфейса «Готовность ВУ». При записи очередного байта в буферный регистр A1 обнуляется регистр состояния А2.

Программа записи байта данных в буферный регистр аналогична программе из примера 2.1 за исключением команды перехода: вместо команды JNZ m1 (переход, если не ноль) необходимо использовать команду JZ m1 (переход, если ноль).

Преобразование данных из параллельного формата, в котором они поступили в буферный регистр контроллера из системного интерфейса, в последовательный и передача их на линию связи производятся в сдвиговом регистре с помощью генератора тактовых импульсов и двоичного трехразрядного счетчика импульсов следующим образом.

Последовательная линия связи контроллера с ВУ подключается к выходу младшего разряда сдвигового регистра. По очередному тактовому импульсу содержимое сдвигового регистра сдвигается на один разряд вправо и в линию связи «Данные» выдается значение очередного разряда. Одновременно со сдвигом в ВУ передается по отдельной линии «Синхронизация» тактовый импульс. Таким образом, каждый передаваемый по линии «Данные» бит информации сопровождается синхронизирующим сигналом по линии «Синхронизация», что обеспечивает его однозначное восприятие на приемном конце последовательной линии связи.

Количество переданных в линию тактовых сигналов, а следовательно, и переданных бит информации подсчитывается счетчиком тактовых импульсов. Как только содержимое счетчика становится равным 7, т. е. в линию переданы 8 бит (1 байт) информации, формируется управляющий сигнал «Загрузка», обеспечивающий запись в сдвиговый регистр очередного байта из буферного регистра. Этим же управляющим сигналом устанавливается в «1» регистр состояния. Очередным тактовым импульсом счетчик будет сброшен в «0», и начнется очередной цикл выдачи восьми битов информации из сдвигового регистра в линию связи.

Синхронная последовательная передача отдельных битов данных на линию связи должна производиться без какого-либо перерыва, и следующий байт данных должен быть загружен в буферный регистр из системного интерфейса за время, не превышающее времени передачи восьми битов в последовательную линию связи.

При записи байта данных в буферный регистр обнуляется регистр состояния контроллера. Нуль в этом регистре указывает, что в линию связи передается байт данных из сдвигового регистра, а следующий передаваемый байт данных загружен в сдвиговый регистр.

Контроллер для последовательного синхронного приема данных из ВУ состоит из тех же компонентов, что и контроллер для синхронной последовательной передачи, за исключением генератора тактовых импульсов.

Асинхронный последовательный интерфейс

Организация асинхронного последовательного обмена данными с внешним устройством осложняется тем, что на передающей и приемной стороне последовательной линии связи используются настроенные на одну частоту, но физически разные генераторы тактовых импульсов и, следовательно, общая синхронизация отсутствует. Рассмотрим на примерах организацию контроллеров последовательных интерфейсов для последовательных асинхронных передачи и приема данных.

Простейший контроллер для асинхронной передачи данных в ВУ по последовательной линии связи представлен на рис. 3.8. Он предназначен для передачи данных в формате с двумя стоповыми битами.

Рис. 3.8. Контроллер последовательной асинхронной передачи

На выходной линии контроллера «Данные» поддерживается состояние 0 (значение стартового бита) до тех пор, пока не будет выработан первый импульс сдвига. Импульс сдвига изменит состояние счетчика импульсов сдвига и перепишет в нулевой разряд сдвигового регистра первый информационный бит передаваемого байта данных. Состояние, соответствующее значению этого бита, будет поддерживаться на линии «Данные» до следующего импульса сдвига.

Аналогично будут переданы остальные информационные биты, первый стоповый бит и, наконец, второй стоповый бит, при передаче которого счетчик импульсов сдвига снова установится в нулевое состояние. Это приведет к записи 1 в регистр состояния А2. Единичный сигнал с выхода регистра А2 запретит формирование импульсов сдвига, а также информирует процессор о готовности к приему нового байта данных. После завершения передачи очередного кадра (стартового бита, информационного байта и двух стоповых бит) контроллер поддерживает в линии связи уровень логической единицы (значение второго стопового бита).

Рис. 3.9. Контроллер последовательного асинхронного приема

Уровень логической единицы поступает по линии «Данные» в контроллер для асинхронного приема данных (рис. 3.9). Этот уровень создает условия для выработки сигнала, запрещающего работу делителя частоты генератора тактовых импульсов. Действительно, после приема предыдущего байта данных счетчик импульсов сдвига (счетчик по mod 9) находится в нулевом состоянии и на вентиль И поступают два единичных сигнала: со счетчика сдвигов и из линии «Данные». На выходе вентиля И вырабатывается сигнал сброса делителя частоты сигналов тактового генератора, запрещающий формирование импульсов сдвига.

В момент смены стопового бита на стартовый бит (момент начала передачи нового кадра) на линии «Данные» появится уровень логического нуля и тем самым будет снят сигнал сброса с делителя частоты. Состояние 4-разрядного двоичного счетчика (делителя частоты) начнет изменяться. Когда на счетчике накопится значение 8, он выдаст сигнал, поступающий на входы сдвигового регистра и счетчика импульсов сдвига. Так как частота сигналов генератора тактовых импульсов приемника должна совпадать с частотой генератора тактовых импульсов передатчика, то сдвиг (считывание) бита произойдет примерно на середине временного интервала, отведенного на передачу бита данных, т. е. времени, необходимого для выработки шестнадцати тактовых импульсов. Это делается для уменьшения вероятности ошибки из-за возможного различия частот генераторов передатчика и приемника, искажения формы передаваемых сигналов (переходные процессы) и т. п. Следующий сдвиг произойдет после прохождения шестнадцати тактовых импульсов, т. е. на середине временного интервала передачи первого информационного бита.

При приеме в сдвиговый регистр девятого бита кадра (восьмого информационного бита) из него «выдвинется» стартовый бит и, следовательно, в сдвиговом регистре будет размещен весь принятый байт информации. В этот момент счетчик импульсов сдвига придет в нулевое состояние и на его выходе будет выработан единичный сигнал, по которому содержимое сдвигового регистра перепишется в буферный регистр, в регистр состояния А2 запишется 1 и он будет информировать процессор об окончании приема очередного байта, вентиль И подготовится к выработке сигнала «Сброс» (этот сигнал сформируется после прихода первого стопового бита).

Получив сигнал готовности (1 в регистре А2), процессор выполнит команду «Ввод» (см. пример 2.2 Параллельной передачи данных). При этом вырабатывается управляющий сигнал системного интерфейса «Ввод», по которому производятся пересылка принятого байта данных из буферного регистра в процессор (сигнал «Чтение») и сброс регистра состояния А2.

Отметим, что для простоты изложения в контроллере на рис. 14 не показаны схемы контроля стоповых бит принимаемого кадра. Не показаны также схемы контроля четности или нечетности (паритета) передаваемой информации (обычно в передаваемом байте восьмому биту придается значение 0 или 1, так чтобы в этом байте было четное количество единиц). В реальных контроллерах имеются такие схемы, и если контроллер не принимает из линии связи нужного количества стоповых бит или вырабатывается сигнал ошибки паритета в схеме контроля четности, то принятые в текущем кадре биты данных игнорируются и контроллер ожидает поступления нового стартового бита.

В современных микроЭВМ применяют, как правило, универсальные контроллеры для последовательного ВВ, обеспечивающие как синхронный, так и асинхронный режим обмена данными с ВУ.

Интерфейсы микроконтроллеров (Часть 1)

Итак что же такое интерфейс?

Вездесущая Википедия дает такой ответ: Физический (аппаратный) интерфейс — способ взаимодействия физических устройств. Чаще всего речь идёт о компьютерных портах.

Т.е. если мы попытаемся связать наш микроконтроллер с другими устройствами нам потребуется знать определенный набор правил, методов и характеристик оборудования, чтобы сделать это безболезненно. Давайте рассмотрим основные типы интерфейсов, которые мы можем встретить «на борту» микроконтроллера.

Последовательный интерфейс UART/USART

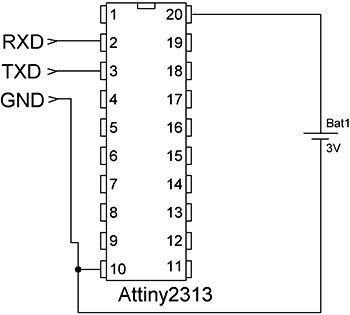

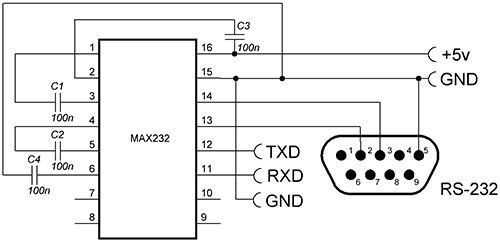

Подключать UART надо, так сказать «наоборот» RXD к TXD, а TXD к RXD как на картинке ниже:

Все сигналы UART передаются специально выбранными уровнями, обеспечивающими высокую помехоустойчивость связи. Отметим, что данные передаются в инверсном коде (логической единице соответствует низкий уровень, логическому нулю — высокий уровень. Более подробно о логических уровнях смотрите тут — www.drive2.ru/b/2528993/).

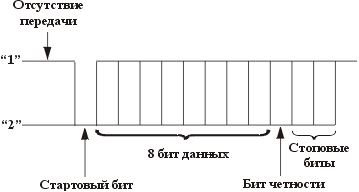

Формат передаваемых данных показан на рисунке 4. Собственно данные (5, 6, 7 или 8 бит) сопровождаются стартовым битом, битом четности и одним или двумя стоповыми битами. Получив стартовый бит, приемник выбирает из линии биты данных через определенные интервалы времени. Очень важно, чтобы тактовые частоты приемника и передатчика были одинаковыми, допустимое расхождение — не более 10%). Скорость передачи по RS-232C может выбираться из ряда: 110, 150, 300, 600, 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200 бит/с.

Последовательный периферийный интерфейс SPI

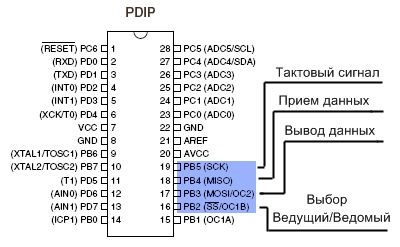

Последовательный периферийный трехпроводный интерфейс SPI (Serial Peripheral Interface) предназначен для организации обмена данными между двумя устройствами. С его помощью может осуществляться обмен данными между микроконтроллером и различными устройствами, такими, как цифровые потенциометры, ЦАП/АЦП, FLASH-ПЗУ и др. С помощью этого интерфейса удобно производить обмен данными между несколькими микроконтроллерами AVR.

Кроме того, через интерфейс SPI может осуществляться программирование микроконтроллера.

Изначально он был придуман компанией Motorola, а в настоящее время используется в продукции многих производителей. Его наименование является аббревиатурой от ‘Serial Peripheral Bus’, что отражает его предназначение — шина для подключения внешних устройств. Шина SPI организована по принципу ‘ведущий-подчиненный’. В качестве ведущего шины обычно выступает микроконтроллер, но им также может быть программируемая логика, DSP-контроллер или специализированная ИС. Подключенные к ведущему шины внешние устройства образуют подчиненных шины. В их роли выступают различного рода микросхемы, в т.ч. запоминающие устройства (EEPROM, Flash-память, SRAM), часы реального времени (RTC), АЦП/ЦАП, цифровые потенциометры, специализированные контроллеры и др.

Главным составным блоком интерфейса SPI является обычный сдвиговый регистр, сигналы синхронизации и ввода/вывода битового потока которого и образуют интерфейсные сигналы. Таким образом, протокол SPI правильнее назвать не протоколом передачи данных, а протоколом обмена данными между двумя сдвиговыми регистрами, каждый из которых одновременно выполняет и функцию приемника, и функцию передатчика. Непременным условием передачи данных по шине SPI является генерация сигнала синхронизации шины. Этот сигнал имеет право генерировать только ведущий шины и от этого сигнала полностью зависит работа подчиненного шины.

Электрическое подключение

Существует три типа подключения к шине SPI, в каждом из которых участвуют четыре сигнала.

Самое простое подключение, в котором участвуют только две микросхемы, показано на рисунке 6. Здесь, ведущий шины передает данные по линии MOSI синхронно со сгенерированным им же сигналом SCLK, а подчиненный захватывает переданные биты данных по определенным фронтам принятого сигнала синхронизации. Одновременно с этим подчиненный отправляет свою посылку данных. Представленную схему можно упростить исключением линии MISO, если используемая подчиненная ИС не предусматривает ответную передачу данных или в ней нет потребности. Одностороннюю передачу данных можно встретить у таких микросхем как ЦАП, цифровые потенциометры, программируемые усилители и драйверы. Таким образом, рассматриваемый вариант подключения подчиненной ИС требует 3 или 4 линии связи. Чтобы подчиненная ИС принимала и передавала данные, помимо наличия сигнала синхронизации, необходимо также, чтобы линия SS была переведена в низкое состояние. В противном случае, подчиненная ИС будет неактивна. Когда используется только одна внешняя ИС, может возникнуть соблазн исключения и линии SS за счет жесткой установки низкого уровня на входе выбора подчиненной микросхемы. Такое решение крайне нежелательно и может привести к сбоям или вообще невозможности передачи данных, т.к. вход выбора микросхемы служит для перевода ИС в её исходное состояние и иногда инициирует вывод первого бита данных.

При необходимости подключения к шине SPI нескольких микросхем используется либо независимое (параллельное) подключение (рис. 7), либо каскадное (последовательное) (рис. 8).

Вспомогательные аппаратные средства микроконтроллера

4.10. Дополнительные модули МК

Описанные выше модули составляют так называемый базовый комплект МК и входят в состав любого современного контроллера. Очевидна необходимость включения в состав МК дополнительных модулей, состав и возможности которых определяются конкретной решаемой задачей. Среди таких дополнительных модулей следует, прежде всего, отметить:

4.10.1. Модули последовательного ввода/вывода

Наличие в составе 8-разрядного МК модуля контроллера последовательного ввода/вывода стало в последнее время обычным явлением. Задачи, которые решаются средствами модуля контроллера последовательного ввода/вывода, можно разделить на три основные группы:

С точки зрения организации обмена информацией упомянутые типы интерфейсов последовательной связи отличаются режимом передачи данных (синхронный или асинхронный), форматом кадра (число бит в посылке при передаче байта полезной информации) и временными диаграммами сигналов на линиях (уровни сигналов и положение фронтов при переключениях).

Число линий, по которым происходит передача в последовательном коде, обычно равно двум (I 2 C, RS-232C, RS-485) или трем (SPI, некоторые нестандартные протоколы). Данное обстоятельство позволяет спроектировать модули контроллеров последовательного обмена таким образом, чтобы с их помощью на аппаратном уровне можно было реализовать несколько типов последовательных интерфейсов. При этом режим передачи (синхронный или асинхронный) и формат кадра поддерживаются на уровне логических сигналов, а реальные физические уровни сигналов для каждого интерфейса получают с помощью специальных ИС, которые называют приемопередатчиками, конверторами, трансиверами.

Среди различных типов встроенных контроллеров последовательного обмена, которые входят в состав тех или иных 8-разрядных МК, сложился стандарт «де-факто» — модуль UART (Universal Asynchronous Receiver and Transmitter). UART — это универсальный асинхронный приемопередатчик. Однако большинство модулей UART, кроме асинхронного режима обмена, способны также реализовать режим синхронной передачи данных.

Не все производители МК используют термин UART для обозначения типа модуля контроллера последовательного обмена. Так, в МК фирмы Motorola модуль асинхронной приемопередачи, который поддерживает те же режимы асинхронного обмена, что и UART, принято называть SCI (Serial Communication Interface). Следует отметить, что модуль типа SCI обычно реализует только режим асинхронного обмена, то есть его функциональные возможности уже по сравнению с модулями типа UART. Однако бывают и исключения: под тем же именем SCI в МК МС68НС705В16 скрывается модуль синхронно-асинхронной передачи данных.

Модули типа UART в асинхронном режиме работы позволяют реализовать протокол обмена для интерфейсов RS-232C, RS-422А, RS-485, в синхронном режиме — нестандартные синхронные протоколы обмена, и в некоторых моделях — SPI. В МК фирмы Motorola традиционно предусмотрены два модуля последовательного обмена: модуль SCI с возможностью реализации только протоколов асинхронной приемопередачи для интерфейсов RS-232C, RS-422A, RS-485 и модуль контроллера синхронного интерфейса в стандарте SPI.

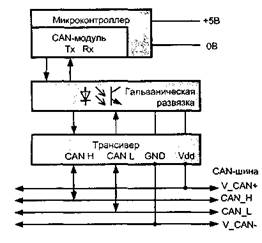

Протоколы интерфейсов локальных сетей на основе МК (I 2 C и CAN) отличает более сложная логика работы. Поэтому контроллеры CAN интерфейса всегда выполняются в виде самостоятельного модуля. Интерфейс I 2 C с возможностью работы как в ведущем, так и ведомом режиме, также обычно поддерживается специальным модулем (модуль последовательного порта в МК 89С52 фирмы Philips). Но если реализуется только ведомый режим I 2 C, то в МК PIC16 фирмы Microchip он успешно сочетается с SPI: настройка одного и того же модуля на один из протоколов осуществляется путем инициализации.

В последнее время появилось большое количество МК со встроенными модулями контроллеров CAN и модулями универсального последовательного интерфейса периферийных устройств USB (Universal Serial Bus). Каждый из этих интерфейсов имеет достаточно сложные протоколы обмена, для ознакомления с которыми следует обращаться к специальной литературе.

4.10.2. Модули аналогового ввода/вывода

Необходимость приема и формирования аналоговых сигналов требует наличия в МК модулей аналогового ввода/вывода.

Простейшим устройством аналогового ввода в МК является встроенный компаратор напряжения. Компаратор сравнивает входное аналоговое напряжение с опорным потенциалом VREF и устанавливает на выходе логическую «1», если входное напряжение больше опорного. Компараторы удобнее всего использовать для контроля определенного значения входного напряжения, например, в термостатах. В комбинации с внешним генератором линейно изменяющегося напряжения встроенный компаратор позволяет реализовать на МК интегрирующий аналого-цифровой преобразователь ( АЦП ).

Собственно аналого-цифровой преобразователь выполнен по методу последовательного приближения. Практически во всех моделях 8-разрядных МК разрядность АЦП также составляет 8 разрядов. Соответственно, формат представления результатов измерения АЦП — однобайтовый. Исключение составляют лишь модули АЦП микроконтроллеров для управления преобразователями частоты для электроприводов, разрешающая способность которых равна 10 разрядам. Два младших разряда результата получают с помощью дополнительного емкостного делителя, не связанного с регистром последовательного приближения.

Момент завершения каждого цикла преобразования отмечается установкой триггера готовности данных. Если прерывания от модуля АЦП разрешены, то генерируется запрос на прерывания. Как правило, чтение регистра результата сбрасывает триггер готовности.

Большинство модулей АЦП имеют только режим программного запуска: установка одного из битов регистра режима запускает очередное измерение. Наиболее универсальные модули АЦП имеют также режим автоматического запуска, при котором после завершения одного цикла преобразования немедленно начинается следующий. Однако данные измерения каждого цикла должны быть считаны программным способом.

Цифро-аналоговые преобразователи в составе МК являются большой редкостью. Функция цифро-аналогового преобразователя реализуется средствами модуля программируемого таймера в режиме ШИМ. На одном из выводов МК формируется высокочастотная импульсная последовательность с регулируемой длительностью импульса. Полученный сигнал сглаживается фильтром нижних частот на операционном усилителе. Разрешающая способность такого ЦАП определяется дискретностью регулирования коэффициента заполнения в режиме ШИМ.

КОНТРОЛЛЕРЫ ПОСЛЕДОВАТЕЛЬНОГО ВВОДА/ВЫВОДА

1)связь встраиваемой МП-системы с системой управления верхнего уровня: промышленным компьютером, программируемым контроллером, офисным компьютером; наиболее часто для этих целей используются интерфейсы RS-232C и RS-485; в настоящее

время все более широкую популярность приобретает интерфейс USB;

2)связь с внешними по отношению к МК периферийными ИС встраиваемой МП-системы, а также с датчиками физических величин с последовательным выходом; для этих

целей используются интерфейсы SPI, I 2 C, а также нестандартные протоколы обмена;

3)интерфейс связи с локальной сетью в мультимикропроцессорных системах; в системах с числом МК до пяти обычно используют сети на основе интерфейсов PC, RS-232C,

RS-485 с собственными сетевыми протоколами верхнего уровня; в более сложных системах все более популярным становится протокол CAN.

С точки зрения инженера-схемотехника, упомянутые типы интерфейсов последовательной связи отличаются: режимом передачи данных (синхронный или асинхронный), форматом кадра (число бит в посылке при передаче байта полезной информации) и временными диаграммами сигналов на линиях (уровни сигналов и положение фронтов при переключениях). Число линий, по которым происходит передача в последовательном коде, обычно равно двум (PC, RS-232C, RS-485, CAN) или трем (SPI, некоторые нестандартные синхронные протоколы). Последнее позволяет спроектировать модули контроллеров последовательного обмена таким образом, чтобы с их помощью на аппаратном уровне можно было бы реализовать несколько типов последовательных интерфейсов. При этом режим передачи (синхронный или асинхронный) и формат кадра поддерживаются на уровне логических сигналов, а реальные физические уровни сигналов, характерные для каждого типа интерфейса, получают с помощью специальных ИС, которые носят название приемопередатчиков, конверторов, трансиверов.

В состав 8-разрядных МК различных фирм производителей входят следующие модули контроллеров последовательных интерфейсов:

• модуль последовательного универсального интерфейса USI (Universal Serial Interface); входит в состав МК семейства AVR фирмы «Atmel»; может поддерживать протоколы асинхронного обмена для интерфейсов RS-232, RS-422 и RS-485, а также синхронные протоколы интерфейсов SPI и I 2 C;

• модуль универсального асинхронного интерфейса UART (Universal Asynchronous Receiver and Transmitter); поддерживает протоколы асинхронного обмена интерфейсов RS-232, RS-422 и RS-485;

• модуль универсального асинхронного интерфейса SCI (Serial Communication Interface); характерен для МК фирмы «Motorola»; входит в состав 8-разрядных МК семейств НС05, НС11 и НС08; является функциональным аналогом модулей типа UART, т. е. Поддерживает протоколы асинхронного обмена для интерфейсов RS-232, RS-422 и RS-485;

• модуль последовательного синхронного интерфейса SPI (Serial Peripheral Interface); поддерживает протокол синхронного обмена в стандарте SPI; интерфейс SPI был предложен фирмой «Motorola», поэтому контроллер SPI входит в состав большого числа моделей МК семейств НС05, НС11 и НС08. В МК других производителей протокол SPI обычно реализуется в качестве альтернативного одним из модулей контроллеров последовательных интерфейсов;

• модуль синхронного последовательного интерфейса PC (Inter Integrated Circuit); входит в состав 8-разрядных МК фирмы «Pfilips» и «Microchip»; следует заметить, что для МК «Microchip» характерна реализация аппаратными средствами одного и того же модуля протоколов SPI и PC;

• модуль контроллера CAN (Control Aria Network); присутствует в 8-разрядных МК семейства НС08 фирмы «Motorola», МК семейства С500 фирмы «Infineon», семейства 89 фирмы «Pfilips»; поддерживает стандартные протоколы обмена CAN сетей;

• модуль контроллера USB (Universal Serial Bus); поддерживает новый стандарт периферийного интерфейса вычислительной техники USB.

Следует заметить, что одноименные модули контроллеров последовательных интерфейсов даже одной фирмы-производителя имеют отличия в реализации для разных семейств МК. Так, аппаратные средства контроллера SCI в составе МК семейства НС08 диагностируют большее количество ошибок на линии, чем одноименные контроллеры в составе семейства НС05. И естественно, отличаются одноименные модули в МК различных фирм. Однако эти отличия преимущественно сводятся к различию регистров специальных функций, которые обслуживают модуль. Меньше затрагивают алгоритмы функционирования одноименных модулей. И, по определению, все аналогичные модули обязательно реализуют на аппаратном уровне логику протокола обмена выбранного интерфейса. Поэтому при рассмотрении данной темы целесообразно остановиться именно на протоколах обмена. По режиму обмена информацией интерфейсы подразделяют на симплексные, полудуплексные, дуплексные, мультиплексные. В интерфейсах с симплексным режимом обмена информацией возможна лишь однонаправленная передача информации от одного абонента к другому. Соответственно и буферы приемника и передатчика информации выполнены однонаправленными. В интерфейсах с полудуплексным режимом обмена в произвольный момент времени может производиться либо только прием, либо только передача данных между двумя абонентами, буферы приемопередатчика каждого из абонентов связи выполнены двунаправленными. В интерфейсах с дуплексным режимом обмена в любой произвольный момент времени может производиться одновременный прием и передача данных между двумя абонентами. Линии приема и передачи информации физически разделены, соответственно контроллер обмена каждого абонента имеет два вывода (приемника и передатчика), и буферы этих выводов однонаправленные. В интерфейсах с мультиплексным режимом обмена в каждый момент времени может осуществляться прием или передача данных между парой любых абонентов сети.

Не все производители МК используют термин UART для обозначения типа модуля контроллера последовательного обмена. Так, в МК фирмы «Motorola» модуль асинхронной приемопередачи, который поддерживает те же режимы асинхронного обмена, что и UART, принято называть SCI (Serial Communication Interface). Следует отметить, что модуль типа SCI обычно реализует только режим асинхронного обмена, однако МК фирмы «Motorola» традиционно имеют в своем составе два модуля последовательного обмена: модуль SCI с возможностью реализации только протоколов асинхронной приемопередачи для интерфейсов RS-232C, RS-422A, RS-485 и модуль контроллера синхронного интерфейса в стандарте SPI.

Модуль типа UART в максимальной конфигурации обычно реализует два типа протокола обмена в асинхронном режиме (кадр длиною в 10 бит или в 11 бит) и два типа протокола в синхронном режиме (трехпроводный полнодуплексный обмен или двухпроводный полудуплексный обмен). Упрощенная структура модуля типа UART приведена на рис. 4.19.

Передача данных от МК к другому устройству инициируется посредством записи байта данных в регистр TDBUF.

Если работа передатчика разрешена (бит ТЕ в регистре управления модулем равен 1), то аппаратные средства модуля загружают содержимое TDBUF в сдвиговый регистр и под управлением генератора скорости обмена биты из сдвигового регистра, начиная с младшего DO, последовательно передаются на вывод TxD МК. По завершении передачи байта данных устанавливается бит TI, который информирует МК о том, что буфер передатчика пуст и в него могут быть загружены новые данные для передачи. Бит TI генерирует запрос на прерывание, если прерывания от передатчика в МК разрешены. Бит TI может также быть считан программно.

Если работа приемника разрешена (бит RE в регистре управления модулем равен 1), то после распознавания стартового бита аппаратные средства приемника преобразуют данные, которые поступают на вход RxD в последовательном коде, в параллельный код. После завершения приема последнего бита в сдвиговом регистре приемника находится принятый байт данных, который автоматически переносится в регистр RDBUF. Одновременно устанавливается в «1» флаг завершения приема RI. Бит RI может быть считан под управлением программы, а если прерывания от приемника разрешены, то генерируется запрос на прерывание. В процессе выполнения подпрограммы прерывания принятый байт данных считывается из регистра данных приемника RDBUF в память МК. Сразу после копирования байта данных из сдвигового регистра в RDBUF приемник может начать формирование следующего байта данных, отдельные биты которого продолжают поступать на вход RxD. Однако необходимо, чтобы центральный процессор МК успел считать данные из буферного регистра RDBUF до завершения формирования в сдвиговом регистре следующего принятого байта. Если этого не произошло, то возникшая аварийная ситуация в модулях UART разрешается различными путями. В модулях SCI фирмы «Motorola» запись следующего принятого байта в буферный регистр данных не производится и устанавливается флаг ошибки OR (Overrun). Этот флаг наравне с триггером RI может генерировать запрос на прерывание от приемника. В модулях МК Intel MSC-51 и ему полностью аналогичных такая защита отсутствует: следующий принятый байт затирает предыдущий в регистре RDBUF.

Для повышения достоверности приема каждого разряда аппаратные средства модуля UART считывают уровень сигнала на входе RxD три раза в течение интервала присутствия бита. Значение бита, которое будет занесено в младший разряд сдвигового регистра приемника, определяется мажоритарным способом: по принципу два из трех. Модули SCI сообщают пользователю о наличии шума на линии приема: если не все три значения при приеме любого из битов кадра совпали, то устанавливается флаг NF (Noise Error). В модулях UART MK Intel MSC-51 такая защита не предусмотрена.

Подсистемы приемника и передатчика модуля UART не являются полностью автономными. Скорость обмена и формат кадра асинхронной приемопередачи назначаются в процессе инициализации модуля одинаковыми для приемника и для передатчика. Модули UART различных МК предоставляют неодинаковые возможности по регулированию скорости обмена. В МК Intel MSC-51 допускается плавное регулирование с дискретностью, равной периоду частоты тактирования таймера. Для задания скорости обмена используется один из каналов модуля таймера. Напротив, модуль SCI МК Motorola не использует ресурсы модуля таймера для этих целей. Такой подход, с одной стороны, имеет преимущество по экономии использования ресурсов МК, однако, с другой стороны, не позволяет задать произвольное соотношение между частотой обмена и собственной частотой кварцевого резонатора генератора синхронизации МК. Последнее накладывает ограничения на выбор частоты кварцевого резонатора, если скорость обмена в разрабатываемом устройстве должна соответствовать стандартному ряду.

Все модули типа UART предусматривают два типа кадров асинхронного обмена, На рис. 4.20 представлена временная диаграмма 10-битового кадра: 8 бит данных передаются вслед за стартовым битом, начиная с младшего DO, завершает передачу стоповый бит

Следует заметить, что не все модули UART 8-разрядных МК имеют опции автоматического формирования бита паритета и не контролируют принятое слово на четность или нечетность аппаратными средствами. Поэтому при необходимости эти операции должны быть реализованы программными средствами. Рассмотренный 10-битовый формат кадра наиболее часто используется при организации связи встраиваемой МП системы с системой управления верхнего уровня.

|

Следующий кадр используются для обмена данными с выбранным ведомым.

|

Рис. 4.22.Структура локальной сети микроконтроллера

Бит D8 этих кадров должен быть установлен в «0». Последний кадр пакета обмена должен содержать 11 нулевых битов. Так как подобная последовательность не может быть сформирована в результате записи в регистр буфера передатчика TDBUF нулевого слова | (необходимо также обнулить стоповый бит), то для ее воспроизведения предусмотрена специальная опция формирования сигнала «Break». В модулях SCI для ее реализации необходимо установить бит SBK (Send Break) в одном из регистров управления. Обмен между ведущим и ведомым происходит в следующем порядке.

• В исходном состоянии приемники всех ведомых МК находятся в состоянии ожидания.

В этом состоянии прием байта данных осуществляется, но принятое слово переписывается в буферный регистр RDBUF с одновременной установкой в «1» флага завершения приема RI только в том случае, если бит D8 этого слова равен «1». Остальные слова с признаком D8 = 0 игнорируются.

• Все ведомые МК принимают это 9-разрядное слово, и, поскольку разряд D8 кадра равен «1», приемник модуля UART каждого МК выходит из состояния ожидания. Формируется запрос на прерывание. Подпрограмма обработки этого прерывания сравнивает принятый адрес с собственным адресом в локальной сети. Если адреса совпадают, т. е. ведущий будет производить обмен именно с этим ведомым, то МК ожидает

передачи от ведомого следующего кадра. Если адреса не совпадают, то МК посредством специального бита управления переводит приемник модуля UART снова в режим ожидания. Тогда все следующие кадры пакета обмена этим МК восприняты не будут, поскольку они содержат нулевой разряд D8.

• Ведущий МК передает ведомому необходимое число байтов, сопровождая каждый из них признаком данных D8 = 0. При необходимости ведущий принимает данные от ведомого. О завершении обмена ведущий информирует ведомый посылкой сигнала «Break».

• Ведомый в ответ на сигнал «Break» переводит приемник модуля UART в состояние ожидания. Локальная сеть приведена в исходное состояние и готова к передаче нового пакета.

Кроме рассмотренных режимов асинхронного обмена, многие из модулей UART поддерживают режим синхронной приемопередачи. Так, вМКМЗС-51 контроллер последовательного интерфейса реализует полудуплексный обмен в синхронном режиме, при котором импульсы синхронизации выдаются на линию TxD, данные передаются или принимаются по линии RxD (см. 4.2.7). Важно отметить, что при синхронном обмене модуль UART МК MSC-51 может работать только в ведущем режиме, т. е. именно этот модуль формирует импульсы синхронизации независимо от направления обмена. Модуль SCI МК МС68НС705В16 (модуль типа UART) реализует симплексный синхронный обмен, при котором возможно только одно направление передачи данных: из МК к периферийной ИС.

|

Рис. 4.23.Сопряжение МК с периферийными ИС посредством интерфейса SPI

В качестве периферийных устройств могут использоваться как простейшие сдвиговые регистры, так и сложные периферийные ИС со встроенными контроллерами управления, такие как ЦАП, сигма-дельта АЦП с цифровой фильтрацией, последовательные запоминающие устройства типа FLASH или EEPROM, энергонезависимые ОЗУ и т. д. В редких случаях интерфейс SPI используется для обмена данными между несколькими МК системы.

На рис. 4.23 представлена структурная схема сопряжения МК и двух периферийных ИС с использованием интерфейса SPI. В рассматриваемом примере МК является ведущим устройством, он инициирует обмен при передаче информации между МК и одной из периферийных ИС. Каждая из периферийных ИС является устройством ведомым. SPI- шина представлена тремя общими линиями связи (MISO, MOSI, SCK) и двумя линиями выбора ведомого устройства (SS1, SS2), которые индивидуальны для каждой периферийной ИС:

SCK-линия сигнала стробирования данных;

SS1 и SS2-линии сигналов выбора ведомого устройства.

|

Схема управления контроллера SPI интерфейса позволяет выбрать один из двух протоколов обмена и полярность импульсов синхронизации SCK. При работе в ведущем режиме возможно также программно выбрать частоту импульсов синхронизации.

Два бита регистра управления любого контроллера SPI интерфейса определяют временную диаграмму обмена по шине SPI:

1) бит СРНА назначает протокол обмена;

2> бит CPOL определяет полярность сигнала синхронизации SCK.

В соответствии с комбинацией битов CPHA:CPOL принято различать четыре режима работы интерфейса SPI. Комбинации CPHA:CPOL = 00 соответствует режим 0, комбинации CPHA:CPOL =11— режим 3. Встроенный контроллер SPI МК позволяет программно настраивать режим SPI в процессе инициализации, в то время как периферийные ИС реализуют один или два режима SPI, которые определяются их техническим описанием. Наиболее часто это режимы 0 и 3.

На рис. 4.25 представлены временные диаграммы сигналов для протокола передачи СРНА = 0. Для сигнала SCK приводятся две диаграммы, различающиеся полярностью сигнала.

Начало обмена рассматриваемого протокола определяется установкой сигнала выбора ведомого SS в активное состояние SS = 0. При направлении передачи от ведущего к ведомому первый перепад сигнала синхронизации SCK используется ведомым устройством для запоминания очередного бита во внутреннем сдвиговом регистре контроллера SPI. Ведущий выставляет очередной бит посылки на линии MOSI по каждому четному фронту сигнала SCK. При передаче данных от ведомого к ведущему старший бит передаваемого байта должен быть выставлен ведомым на линию MISO сразу после изменения уровня сигнала SS = 0. По первому фронту SCK уровень сигнала на линии MISO будет запомнен в младшем разряде сдвигового регистра ведущего устройства. По этой причине сигнал на линии выбора ведущего должен быть возвращен в неактивное состояние SS = 1 после передачи каждого байта в любом направлении. Тогда передача каждого нового байта будет сопровождаться предварительной

Начало обмена для протокола опции СРНА = 1 (рис. 4.26) определяет первое изменение уровня сигнала на линии SCK после установки сигнала выбора ведомого SS в активное состояние SS = 0. При передаче данных от ведущего к ведомому и в обратном направлении все нечетные перепады SCK вызывают выдвижение очередного бита посылки из сдвигового регистра передатчика на линию. Каждый четный перепад используется для записи этого бита в сдвиговый регистр приемника. Сигнал выбора ведомого может оставаться в активном состоянии SS = 0 в течение передачи нескольких байт информации. Это несколько упрощает логику программного драйвера SPI.

Рассмотренные протоколы обмена не имеют различий по скорости и надежности передачи информации. Выбор протокола диктуется периферийным устройством. В некоторых случаях полярность и фаза сигнала SCK изменяются между передачами для того, чтобы обеспечить связь с устройствами, имеющими различный протокол. Пример контроллера SPI рассмотрен в п. 4.3.9.

Интерфейс I 2 C является двухпроводным последовательным интерфейсом, разработанным фирмой «Philips Corporation».

Основными свойствами интерфейса PC являются следующие:

• двунаправленная передача данных между главными и подчиненными устройствами;

• многоабонентская шина (центрального главного узла в сети может не быть);

• арбитраж между одновременно передающими устройствами без разрушения целостности передаваемых данных;

• последовательная тактовая синхронизация позволяет приборам с различными скоростями передачи битов осуществлять связь через одну последовательную шину;

• последовательная тактовая синхронизация может использоваться в качестве механизма квитирования установления связи, чтобы приостанавливать и возобновлять последовательную передачу.

Магистраль интерфейса I 2 C использует две линии для передачи информации между приборами:

Типовая конфигурация PC-шины показана на рис. 4.27.

В зависимости от направления передачи возможны два типа обмена данными для I 2 C шины.

1.Передача данных от главного передатчика к подчиненному приемнику. Первый байт,передавае-

мый передатчиком, является адресом подчиненного приемника. Затем следует несколько байтов данных. Подчиненный приемник возвращает бит подтверждения после каждого принятого байта.

2.Передача данных от подчиненного передатчика к главному приемнику. Первый байт

(адрес подчиненного передатчика) передается главным устройством. Затем подчиненный передатчик возвращает бит подтверждения. Следующие несколько байтов данных

передаются подчиненным устройством главному. Главное устройство возвращает бит

подтверждения после каждого принятого байта, кроме последнего. В конце последнего

принятого байта возвращается «нет подтверждения».

Когда нет передачи данных, реализуется режим ожидания: линии тактирования SCL и данных SDA приведены подтягивающими резисторами к высокому уровню логического сигнала.

Модуль контроллера интерфейса 1 2 С, который удовлетворяет спецификации 1 2 С-шины и поддерживает два вышеперечисленных типа передачи данных, может работать в следующих четырех режимах.

1.Режим главного передатчика. Последовательный вывод данных через выход SDA

передатчика, в то время как на выходе SCL передатчика формируются последовательные синхроимпульсы. Первый переданный байт содержит адрес подчиненного приемного устройства (7 бит) и бит направления данных R/W = 0. В этом случае говорят, что

передается «W». Таким образом, первый переданный байт представляет собой адрес

подчиненного приемника плюс «W». Последовательные данные передаются по 8 бит.

После отправки каждого байта главный передатчик ожидает от подчиненного устройства

бит подтверждения ASK. Условия START и STOP формируются ведущим (главным)

устройством для указания начала и конца сеанса последовательного обмена посылкой,

состоящей в общем случае из нескольких байтов.

2.Режим главного приемника. Первый переданный приемником байт содержит адрес подчиненного передающего устройства (7 бит) и бит направления данных R/W = 1.

В этом случае говорят, что передается «R». Таким образом, первый переданный приемником байт представляет собой адрес подчиненного передатчика плюс «R». Последовательные данные передаются по линии SDA от ведомого (подчиненного) устройства

к ведущему (главному), в то время как импульсы синхронизации на линии SCL формирует ведущий. Последовательные данные передаются по 8 бит. После того, как ведущий

(главный) принял очередной байт, он выставляет на линию сигнал подтверждения приема ASK. Сигналы START и STOP формируются ведущим.

3.Режим подчиненного приемника. Последовательные данные и синхроимпульсы передаются по линиям SDA и SCL на одноименные входы подчиненного приемника. После

того, как принят каждый байт, приемник анализирует наличие на линии бита подтверждения ASK, который формирует передатчик. Условия START и STOP формируются передатчиком. Распознавание адреса выполняется аппаратными средствами модуля приемника

после приема адреса подчиненного устройства и бита направления.

4. Режим подчиненного передатчика. Первый байт принимается и обрабатывается

подчиненным передатчиком так же, как и в режиме подчиненного приемника. Однако бит

направления в принятом байте будет указывать, что направление обмена должно быть

изменено на обратное. Далее последовательные данные передаются по линии SDA

с одноименного выхода подчиненного (ведомого) передатчика, в то время как синхроимпульсы принимаются им по входу SCL от главного приемника. После передачи каждого

байта подчиненный передатчик анализирует наличие на линии бита подтверждения ASK.

Условия START и STOP формирует главный приемник.

В подчиненном режиме аппаратные средства контроллера PC-интерфейса осуществляют поиск своего собственного подчиненного адреса или адреса общего вызова. Если детектируется один из этих адресов, запрашивается прерывание. Когда микроконтроллер желает, чтобы шина стала главной, аппаратные средства ожидают, пока шина освободится. Возможное функционирование в качестве подчиненного при этом не прерывается. Если арбитраж шины потерян в главном режиме, то соответствующий контроллер PC переключается в подчиненный режим немедленно и может детектировать свой собственный подчинённый адрес

|

Структура CAN-сети представлена на рис. 4.30. Шинная топология, являющаяся основой CAN, требует наличия механизма адресации узлов, однако в CAN нет адресов как таковых: сообщение принимается всеми узлами. Любое передаваемое сообщение имеет определяющий его содержание уникальный идентификатор (ID), на основании которого каждый узел фильтрует «свои» сообщения и «решает», реагировать или нет на сообщение, транслируемое в данный момент. Неоспоримыми преимуществами отсутствия адресации являются теоретически неограниченное число узлов и простота их добавления и отключения.

|

с 18-битным расширением) с теоретически возможным числом типов сообщений более 536 млн. Фреймы, соответствующие стандартному и расширенному форматам сообщений, приведены на рис. 4.31.

Начинается фрейм доминантным битом SOF (Start of Frame), служащим также для синхронизации битового потока, а заканчивается семью битами рецессивного уровня поля EOF (End of Frame) и 3-битным того же уровня промежутком между фреймами.

|

Сигнализация об ошибках происходит посредством передачи фрейма Error Frame. Он инициируется любым узлом (в CAN правильность передачи контролируется каждым узлом), обнаружившим ошибку.

Для задержки передачи данных или посылки фрейма запроса данных (при неготовности приемника или наличии доминантных бит в промежутке между фреймами) служит фрейм перегрузки Overload Frame. В отличие от фрейма ошибки он не влияет на счетчик ошибок и не вызывает повторную передачу сообщения.

4.2. СЕМЕЙСТВО МК MCS-51 ФИРМЫ «INTEL»

АРХИТЕКТУРА МК 8051 АН

На рис. 4.32 приведена внутренняя структура МК 8051 АН фирмы «Intel», с которого началось семейство MCS-51 (отечественный аналог 1816ВЕ51). Контроллер включает следующие модули:

• центральный процессор CPU MCS-51; разрядность обрабатываемого слова составляет один байт;

• внутреннюю память программ объемом 4096 однобайтовых ячеек памяти

• внутреннюю память данных объемом 128 однобайтовых ячеек;

• четыре 8-разрядных параллельных порта ввода/вывода; _

• два 16-разрядных программируемых таймера;

• схему формирования сигналов внешней мультиплексированной магистрали адрес/

данные и внешней магистрали управления.

Обмен информацией между модулями осуществляется по 8-разрядной внутренней магистрали.

МК семейства MCS-51 используют гарвардскую архитектуру: память программ (ПЗУ) и память данных (ОЗУ) имеют раздельное адресное пространство. И, как следствие, для обращения к ячейкам памяти разного типа должны быть использованы разные типы команд. Максимальный размер адресного пространства для каждого типа памяти составляет 64 Кбайта. Однако непосредственно на кристалле МК 8051 АН располагаются только 4 «байта ПЗУ и 128 байт ОЗУ. МК семейства MCS-51 имеют открытую архитектуру, т.е. позволяют подключать внешнюю память. Поэтому при необходимости, как память программ, так и память данных могут быть увеличены посредством подключения дополнительных микросхем памяти.

В каждом из рассмотренных режимов МК 8051 АН может использовать два массива памяти данных: внутреннее ОЗУ, расположенное по адресам 00h. 7Fh, и подключаемое внешнее ОЗУ, или ПЗУ, которое может располагаться, начиная с адреса 0000h вплоть до 0FFFFh. He следует бояться возможного перекрытия адресного пространства внутренней и внешней памяти данных. Доступ к ним осуществляется разными командами.

В архитектуре MCS-51 адресное пространство внутренней памяти данных объединяет все программно доступные ресурсы МК, в том числе регистры центрального процессора. Пространство внутренней памяти данных делится на пространство адресов внутреннего ОЗУ и пространство адресов регистров специальных функций (рис. 4.34).

В области ОЗУ выделяют три сегмента.